Héich Qualitéit Printed Circuit Board PCB

PCB (PCB Assemblée) Prozess Méiglechen stoussen

| Technesch Ufuerderung | Professionell Surface-Montage an Duerch-Lach Löttechnologie |

| Verschidde Gréissten wéi 1206,0805,0603 Komponenten SMT Technologie | |

| ICT(In Circuit Test),FCT(Functional Circuit Test) Technologie | |

| PCB Assemblée Mat UL, CE, FCC, Rohs Genehmegung | |

| Nitrogen Gas Reflow soldering Technologie fir SMT | |

| Héich Standard SMT & Solder Assemblée Linn | |

| Héich Dicht interconnected Board Placement Technologie Kapazitéit | |

| Zitat & Produktioun Ufuerderung | Gerber Datei oder PCB Datei fir Bare PCB Board Fabrikatioun |

| Bom (Bill of Material) fir Assemblée, PNP (Pick and Place Datei) a Komponenten Positioun och gebraucht an der Assemblée | |

| Fir d'Zitatzäit ze reduzéieren, gitt eis w.e.g. déi voll Deelnummer fir all Komponenten, Quantitéit pro Board och d'Quantitéit fir Bestellungen. | |

| Testen Guide & Funktioun Testmethod fir d'Qualitéit ze garantéieren fir bal 0% Schrottrate z'erreechen |

Iwwer

PCB hunn aus Single-Layer zu duebel-dofir entwéckelt, Multi-Layer a flexibel Conseils, a entwéckelen sech permanent an der Richtung vun héich Präzisioun, héich Dicht an héich Zouverlässegkeet. Kontinuéierlech d'Gréisst schrumpfen, d'Käschte reduzéieren an d'Performance verbesseren wäert de gedréckte Circuit Board nach ëmmer eng staark Vitalitéit an der Entwécklung vun elektronesche Produkter an der Zukunft behalen. An Zukunft ass d'Entwécklung Trend vun gedréckte Circuit Verwaltungsrot Fabrikatioun Technologie an der Richtung vun héich Dicht ze entwéckelen, héich Präzisioun, kleng Ouverture, dënn Drot, klenge Pitch, héich Zouverlässegkeet, Multi-Layer, Héich-Vitesse Transmissioun, Liichtjoer Gewiicht an dënn Form.

Detailléiert Schrëtt a Virsiichtsmoossname vun der PCB Produktioun

1. Design

Ier de Fabrikatiounsprozess ufänkt, muss de PCB entworf / Layout vun engem CAD Bedreiwer baséiert op engem Aarbechtskreesschema. Wann den Designprozess fäerdeg ass, gëtt eng Rei vun Dokumenter dem PCB Hiersteller geliwwert. Gerber Dateien sinn an der Dokumentatioun abegraff, déi Layer-by-Layer Konfiguratioun, Drillthrough Dateien, Pick-and-Plazdaten an Textannotatiounen enthält. Veraarbechtung vun Drécker, liwwert Veraarbechtungsinstruktiounen kritesch fir d'Fabrikatioun, all PCB Spezifikatioune, Dimensiounen an Toleranzen.

2. Virbereedung virun der Fabrikatioun

Wann d'PCB-Haus dem Designer säi Dateipaket kritt, kënne se ufänken de Fabrikatiounsprozessplang an d'Artwork Package ze kreéieren. D'Fabrikatiounsspezifikatioune bestëmmen de Plang andeems Dir Saache wéi Materialtyp, Uewerflächefinanz, Plackéierung, Array vun Aarbechtsplacken, Prozessrouting a méi oplëscht. Zousätzlech kann eng Rei vu kierperleche Konschtwierker duerch e Filmplotter erstallt ginn. Artwork wäert all Schichten vun der PCB wéi och Konschtwierker fir soldermask an Begrëff Marquage enthalen.

3. Material Virbereedung

D'PCB Spezifizéierung erfuerderlech vum Designer bestëmmt d'Materialtyp, d'Kärdicke an d'Kupfergewiicht benotzt fir d'Materialpräparatioun unzefänken. Eensäiteg an duebelsäiteg steiwe PCBs erfuerderen keng bannescht Schichtveraarbechtung a ginn direkt an de Buerprozess. Wann de PCB multi-layered ass, gëtt eng ähnlech Materialpräparatioun gemaach, awer a Form vun banneschten Schichten, déi normalerweis vill méi dënn sinn a kënnen op eng virbestëmmte final Dicke (Stackup) opgebaut ginn.

Eng gemeinsam Produktiounspanelgréisst ass 18 ″x24″, awer all Gréisst kann benotzt ginn soulaang et an de PCB-Fabrikatiounsfäegkeeten ass.

4. Multilayer PCB nëmmen - banneschten Layer Veraarbechtung

Nodeems déi entspriechend Dimensiounen, Materialtyp, Kärdicke a Kupfergewiicht vun der banneschten Schicht virbereet sinn, gëtt se geschéckt fir d'Maschinéiert Lächer ze bueren an dann ze drécken. Béid Säite vun dëse Schichten si mat Photoresist beschichtet. Alignéiert d'Säiten mat banneschten Schichtkonschtwierker an Tool Lächer, exposéiert dann all Säit op UV Liicht mat engem opteschen Negativ vun de Spuren a Featuren, déi fir dës Schicht spezifizéiert sinn. UV-Liicht, déi op de Photoresist fällt, verbënnt d'Chemikalien un d'Kupferfläch, an déi verbleiwen onexposéiert Chemikalie gëtt an engem Entwécklungsbad geläscht.

De nächste Schrëtt ass d'exposéiert Kupfer duerch en Ätzprozess ze läschen. Dëst léisst Kupferspuren ënner der Photoresistschicht verstoppt. Wärend dem Ätzprozess sinn souwuel d'Konzentratioun vum Äss wéi och d'Beliichtungszäit Schlësselparameter. De Resist gëtt dann entlooss, a léisst Spuren a Featuren op der banneschten Schicht.

Déi meescht PCB Fournisseuren benotzen automatiséiert optesch Inspektiounssystemer fir Schichten a Post-Etch-Punchen z'inspektéieren fir Laminéierungsinstrument Lächer ze optimiséieren.

5. Multilayer PCB nëmmen - Laminat

E virbestëmmte Stack vum Prozess gëtt während dem Designprozess etabléiert. De Laminéierungsprozess gëtt an engem proppere Raumëmfeld mat enger kompletter bannenzeger Schicht, Prepreg, Kupferfolie, Pressplacken, Pins, Edelstahl-Spaceer a Backingplaten duerchgefouert. All Press Stack kann aménagéieren 4 ze 6 Brieder pro Press Ouverture, jee no der Dicke vun der fäerdeg PCB. E Beispill vun engem 4-Schicht Board Stackup wier: Platen, Stahlseparator, Kupferfolie (4. Schicht), Prepreg, Kär 3-2 Schichten, Prepreg, Kupferfolie a widderhuelen. Nodeems 4 bis 6 PCBs versammelt sinn, befestegt eng Top-Plack a setzt se an der Laminéierungspress. D'Press rampéiert bis op d'Konturen a setzt Drock op bis de Harz schmëlzt, op deem Punkt de Prepreg fléisst, d'Schichten zesummen an d'Press killt. Wann erausgeholl a prett ass

6. Bueraarbechten

De Buerprozess gëtt vun enger CNC-kontrolléierter Multi-Statioun Buermaschinn ausgeführt, déi eng héich RPM-Spindel an e Karbidbohrer benotzt fir PCB Bueraarbechten. Typesch Vias kënne sou kleng sinn wéi 0,006 ″ bis 0,008 ″ mat Geschwindegkeeten iwwer 100K RPM gebohrt.

De Buerprozess erstellt eng propper, glat Lachmauer déi déi bannescht Schichten net beschiedegt, awer d'Buerung bitt e Wee fir d'Verbindung vun den banneschten Schichten no der Plackéierung, an dat net duerch Lach endet Heem fir duerch-Lach Komponenten.

Net-platéiert Lächer ginn normalerweis als sekundär Operatioun gebuer.

7. Kofferplating

Electroplating gëtt wäit an der PCB Produktioun benotzt wou plated duerch Lächer erfuerderlech sinn. D'Zil ass eng Schicht vu Kupfer op engem konduktiven Substrat duerch eng Serie vu chemesche Behandlungen ze deposéieren, an dann duerch spéider Elektroplatéierungsmethoden fir d'Dicke vun der Kupferschicht op eng spezifesch Designdicke ze erhéijen, typesch 1 mil oder méi.

8. Bausseschichtbehandlung

Déi baussenzeg Schichtveraarbechtung ass tatsächlech d'selwecht wéi de Prozess virdru beschriwwen fir déi bannescht Schicht. Béid Säiten vun der ieweschter an ënnen Schichten si mat Photoresist beschichtet. Alignéiert d'Säiten mat äusseren Artwork an Tool Lächer, setzt dann all Säit op UV Liicht aus fir den opteschen negativen Muster vu Spuren a Featuren ze detailléiert. UV-Liicht, déi op de Photoresist fällt, verbënnt d'Chemikalien un d'Kupferfläch, an déi verbleiwen onexposéiert Chemikalie gëtt an engem Entwécklungsbad geläscht. De nächste Schrëtt ass d'exposéiert Kupfer duerch en Ätzprozess ze läschen. Dëst léisst Kupferspuren ënner der Photoresistschicht verstoppt. De Resist gëtt dann entlooss, a léisst Spueren an Features op der äusserer Schicht. Bausseschichtdefekte kënne virum Lötmaske mat enger automatiséierter optescher Inspektioun fonnt ginn.

9. Solder Paste

Solder Mask Applikatioun ass ähnlech wéi bannenzeg a baussenzeg Schichtprozesser. Den Haaptunterschied ass d'Benotzung vun enger photoimageable Mask amplaz Photoresist iwwer d'ganz Uewerfläch vum Produktiounspanel. Benotzt dann d'Konschtwierk fir Biller op der ieweschter an ënnen Schichten ze huelen. No der Belaaschtung gëtt d'Maske am Bildgebitt ofgeschnidden. Den Zweck ass nëmmen d'Gebitt auszesetzen, wou d'Komponente plazéiert a solderéiert ginn. D'Mask limitéiert och d'Uewerflächefinanz vum PCB op déi ausgesat Gebidder.

10. Uewerfläch Behandlung

Et gi verschidde Méiglechkeeten fir d'Finale Surface Finish. Gold, Sëlwer, OSP, Bläi-gratis solder, Bläi-haltege solder, etc.. All dës sinn valabel, awer wierklech kachen op Design Ufuerderunge. Gold a Sëlwer ginn duerch Elektroplatéierung applizéiert, während Bleifräi a Bläi-enthale Solder horizontal duerch waarm Loftsolder applizéiert ginn.

11. Nomenclature

Déi meescht PCBs sinn op de Marquage op hirer Uewerfläch geschützt. Dës Marquage ginn haaptsächlech am Montageprozess benotzt an enthalen Beispiller wéi Referenzmarkéierungen a Polaritéitsmarkéierungen. Aner Marquage kann esou einfach sinn wéi Deelnummer Identifikatioun oder Fabrikatioun Datum Coden.

12. Ënner-Verwaltungsrot

PCBs ginn a voller Produktiounsplacke produzéiert, déi aus hire Fabrikatiounskonturen geplënnert musse ginn. Déi meescht PCBs ginn an Arrays opgestallt fir d'Versammlungseffizienz ze verbesseren. Et kann eng onendlech Unzuel vun dësen Arrays sinn. Kann net beschreiwen.

Déi meescht Arrays ginn entweder op enger CNC-Mühle mat Carbide-Tools geprägt oder mat diamantbeschichtete serrated Tools geschoss. Béid Methode si valabel, an d'Wiel vun der Method gëtt normalerweis vun der Assemblée Team festgeluegt, déi normalerweis d'Array an engem fréie Stadium guttgeheescht.

13. Test

PCB Hiersteller benotzen typesch eng fléien Sonde oder Bett vun Nägel Testprozess. Testmethod bestëmmt duerch Produktquantitéit an / oder verfügbar Ausrüstung

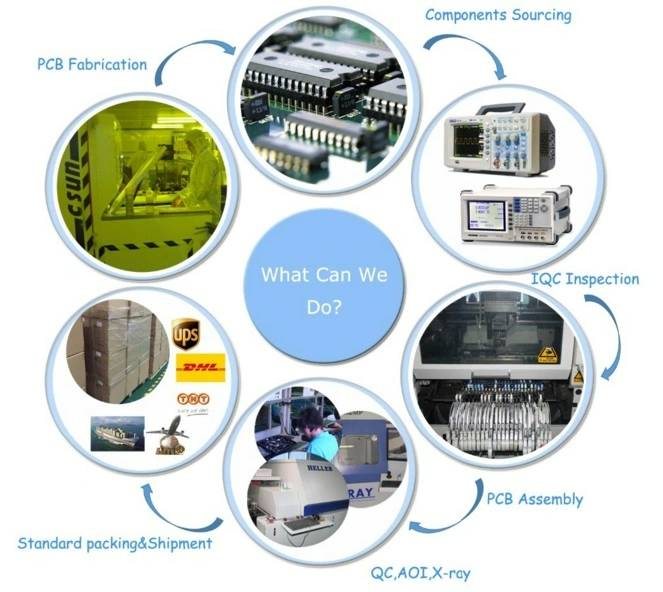

One-Stop Léisung

Factory Show

Eise Service

1. PCB Assemblée Services: SMT, DIP & THT, BGA Reparatur an reballing

2. ICT, konstante Temperatur Burn-an an Funktioun Test

3. Schabloun, Kabel an Uschloss Gebai

4. Standard Verpakung an Op Zäit Liwwerung